Michigan Technological University Digital Commons @ Michigan Tech

Dissertations, Master's Theses and Master's Reports

2016

### SCALABLE INTEGRATED CIRCUIT SIMULATION ALGORITHMS FOR ENERGY-EFFICIENT TERAFLOP HETEROGENEOUS PARALLEL COMPUTING PLATFORMS

Lengfei Han Michigan Technological University, lengfeih@mtu.edu

Copyright 2016 Lengfei Han

#### **Recommended Citation**

Han, Lengfei, "SCALABLE INTEGRATED CIRCUIT SIMULATION ALGORITHMS FOR ENERGY-EFFICIENT TERAFLOP HETEROGENEOUS PARALLEL COMPUTING PLATFORMS", Open Access Dissertation, Michigan Technological University, 2016. https://doi.org/10.37099/mtu.dc.etdr/86

Follow this and additional works at: https://digitalcommons.mtu.edu/etdr Part of the <u>Electronic Devices and Semiconductor Manufacturing Commons</u>

### SCALABLE INTEGRATED CIRCUIT SIMULATION ALGORITHMS FOR ENERGY-EFFICIENT TERAFLOP HETEROGENEOUS PARALLEL COMPUTING PLATFORMS

By Lengfei Han

#### A DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY

In Computer Engineering

# MICHIGAN TECHNOLOGICAL UNIVERSITY 2016

$\bigodot$  2016 Lengfei Han

This dissertation has been approved in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY in Computer Engineering.

Department of Electrical and Computer Engineering

| Dissertation Advisor: | Dr. Zhuo Feng          |

|-----------------------|------------------------|

| Committee Member:     | Dr. Kuilin Zhang       |

| Committee Member:     | Dr. Zhenlin Wang       |

| Committee Member:     | Dr. Zhengfu Xu         |

| Department Chair:     | Dr. Daniel R. Fuhrmann |

## Dedication

To my parents, wife and son

# Contents

| Li                        | st of | Figur   | es                                                       | xi   |

|---------------------------|-------|---------|----------------------------------------------------------|------|

| Li                        | st of | Table   | s                                                        | xiii |

| $\mathbf{P}_{\mathbf{I}}$ | refac | е       |                                                          | xv   |

| A                         | ckno  | wledgr  | ments                                                    | xvii |

| A                         | bstra | ct.     |                                                          | xix  |

| 1                         | Intr  | oduct   | $\mathbf{ion}$                                           | 1    |

|                           | 1.1   | Post-l  | ayout RF Circuits Harmonic Balance Analysis              | 3    |

|                           | 1.2   | Reliat  | pility and Yield Analysis of Small Circuit               | 5    |

|                           | 1.3   | Overv   | riew of Chapters                                         | 7    |

| <b>2</b>                  | Sca   | lable I | Harmonic Balance Analysis of Post-Layout RF Circuits     |      |

|                           | Lev   | eragin  | g Heterogeneous Platform                                 | 9    |

|                           | 2.1   | Backg   | ground and Overview                                      | 9    |

|                           |       | 2.1.1   | Review of Harmonic Balance Analysis                      | 10   |

|                           |       | 2.1.2   | Graph-based Preconditioning Approaches                   | 13   |

|                           |       |         | 2.1.2.1 Graph Sparsification Problems                    | 13   |

|                           |       |         | 2.1.2.2 Ultra-sparsifier Support Graph Preconditioners   | 14   |

|                           |       | 2.1.3   | Overview of Proposed Support-Circuit Preconditioning Ap- |      |

|                           |       |         | proach                                                   | 16   |

|                           | 2.2   | Suppo   | ort-circuit Preconditioner for HB Analysis               | 18   |

|     | 2.2.1   | Sparsification of Representative Laplacian Matrices $\ldots$ .                                         | 19       |

|-----|---------|--------------------------------------------------------------------------------------------------------|----------|

|     |         | $2.2.1.1$ Extraction of Representative Laplacian Matrices $% \left( {{{\bf{n}}_{{\rm{s}}}}} \right)$ . | 19       |

|     |         | 2.2.1.2 Sparsification of Representative Laplacian Matrices                                            | 21       |

|     | 2.2.2   | Sparsification Pattern Extraction                                                                      | 22       |

|     | 2.2.3   | HB Jacobian Preconditioner Construction                                                                | 24       |

|     | 2.2.4   | Case Study: Double-balanced Gilbert Mixer Sparsification .                                             | 25       |

| 2.3 | Parall  | el Block Sparse Matrix Direct Solver                                                                   | 27       |

|     | 2.3.1   | LU Data Dependency Analysis                                                                            | 28       |

|     | 2.3.2   | "Fake" Dependencies in LU Factorization                                                                | 29       |

|     | 2.3.3   | Parallel LU Task Scheduling                                                                            | 31       |

|     | 2.3.4   | Test Matrix Factorization                                                                              | 31       |

|     | 2.3.5   | The Sparse Block LU Algorithm                                                                          | 32       |

| 2.4 | Transi  | ient Analysis Guided Sparsification                                                                    | 33       |

|     | 2.4.1   | HB Simulation Runtime Profiling                                                                        | 34       |

|     | 2.4.2   | Runtime Performance Modeling                                                                           | 36       |

|     |         | 2.4.2.1 CPU Only Platform Performance Model                                                            | 38       |

|     |         | 2.4.2.2 CPU-GPU Platform Performance Model                                                             | 38       |

|     | 2.4.3   | Nearly-optimal Sparsification Scheme                                                                   | 40       |

| 2.5 | The S   | calable HB Analysis Algorithm                                                                          | 42       |

| 2.6 | Exper   | iment Result                                                                                           | 45       |

|     | 2.6.1   | Experimental Setup                                                                                     | 45       |

|     | 2.6.2   | Experimental Results                                                                                   | 46       |

|     | 2.6.3   | Scalability                                                                                            | 49       |

| Ма  | aainolu | Repeated Small Circuit Simulation on GPU                                                               | 51       |

|     | v       | -                                                                                                      | 51<br>51 |

| 3.1 | 0       | Nonlinear Circuit Simulation Approaches                                                                | 51<br>51 |

|     | 3.1.1   | Nonlinear Circuit Simulation Approaches                                                                | 51<br>52 |

|     | 3.1.2   | Massively Parallel GPU Computing                                                                       | 52       |

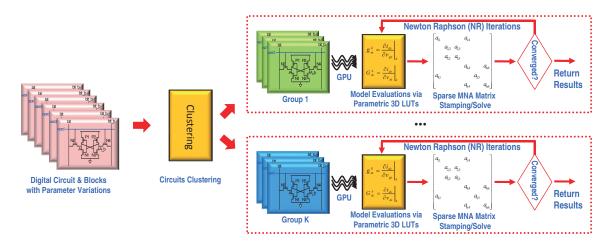

|     | 3.1.3   | Overview of our approach                                                                               | 53       |

3

|   | 3.2 | Device  | e Evaluation and Stamping on GPU                | 55 |

|---|-----|---------|-------------------------------------------------|----|

|   |     | 3.2.1   | Device Evaluation on GPU                        | 55 |

|   |     | 3.2.2   | Jacobian Matrix Data Format and Stamping on GPU | 58 |

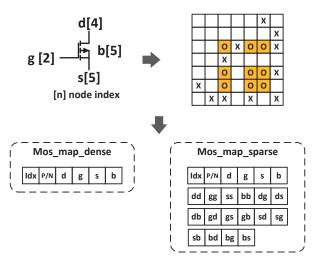

|   |     |         | 3.2.2.1 Dense Jacobian Matrix and Stamping      | 58 |

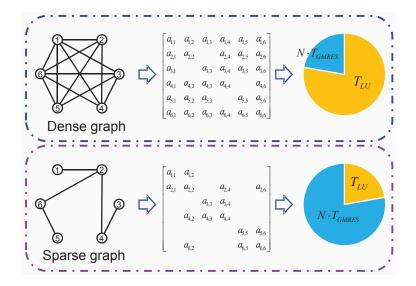

|   |     |         | 3.2.2.2 GPU Sparse Jacobian Matrix and Stamping | 59 |

|   |     | 3.2.3   | RHS and Excitation Sources                      | 61 |

|   | 3.3 | Matri   | x Solver on GPU                                 | 62 |

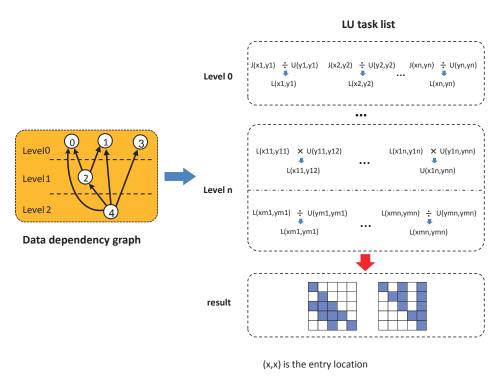

|   |     | 3.3.1   | GPU-based Levelized LU Factorization            | 63 |

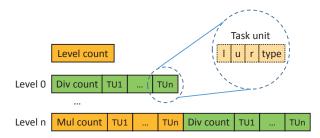

|   |     | 3.3.2   | Circuits Clustering                             | 64 |

|   | 3.4 | GPU     | Optimization                                    | 66 |

|   |     | 3.4.1   | Data Allocation and Access Optimization         | 66 |

|   |     | 3.4.2   | Thread Organization                             | 67 |

|   |     | 3.4.3   | Jacobian Matrix Format Determination            | 69 |

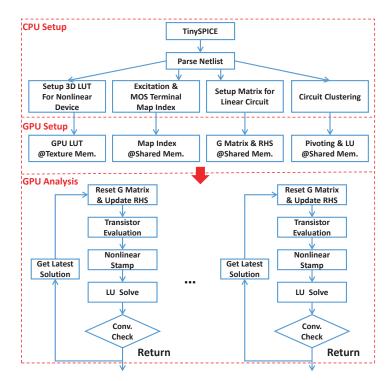

|   | 3.5 | Algori  | thm Flow for TinySPICE                          | 69 |

|   |     | 3.5.1   | CPU and GPU Cooperation                         | 69 |

|   |     |         | 3.5.1.1 CPU Setup Phase                         | 70 |

|   |     |         | 3.5.1.2 GPU setup and analysis phase            | 71 |

|   |     | 3.5.2   | NR Iteration algorithm on GPU                   | 71 |

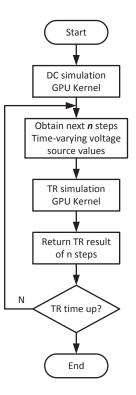

|   |     | 3.5.3   | DC Simulation Flow                              | 72 |

|   |     | 3.5.4   | Transient Simulation Flow                       | 73 |

|   | 3.6 | Exper   | iment Result                                    | 75 |

|   |     | 3.6.1   | Experimental Setup                              | 75 |

|   |     | 3.6.2   | Experimental Results                            | 76 |

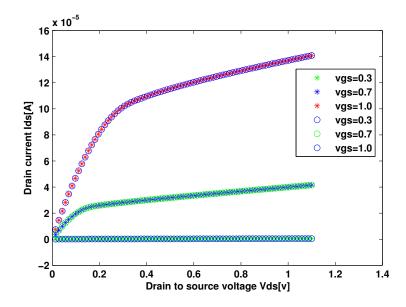

|   |     |         | 3.6.2.1 Accuracy of Parametric 3D LUT           | 76 |

|   |     |         | 3.6.2.2 Runtime Results                         | 79 |

| 4 | Cor | nclusio | n and Future Work                               | 83 |

|   | 4.1 | Concl   | usion of the dissertation                       | 83 |

|   | 4.2 | Future  | e Work                                          | 84 |

| Re           | References |                                  |    |

|--------------|------------|----------------------------------|----|

| $\mathbf{A}$ | Lett       | ers of Permission                | 95 |

|              | A.1        | Permission Letters for Chapter 2 | 95 |

|              | A.2        | Permission Letter for Chapter 3  | 98 |

# List of Figures

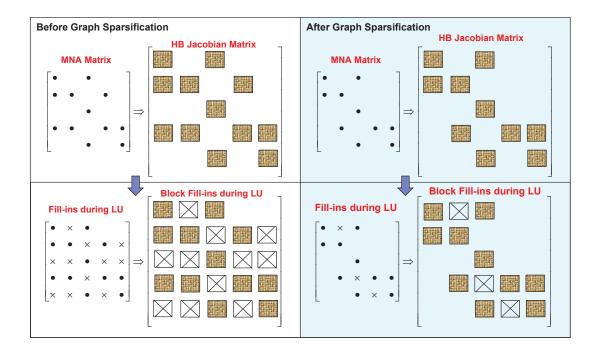

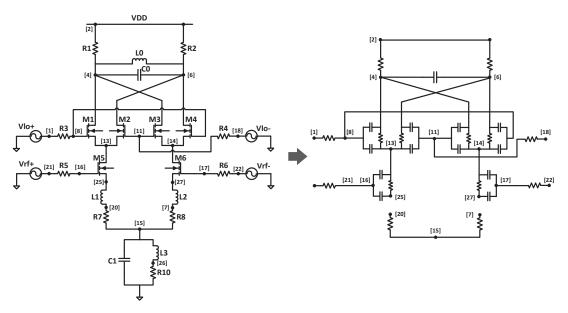

| 2.1  | From sparsification of MNA matrix to sparsification of HB Jacobian                                               |    |

|------|------------------------------------------------------------------------------------------------------------------|----|

|      | matrix problems                                                                                                  | 16 |

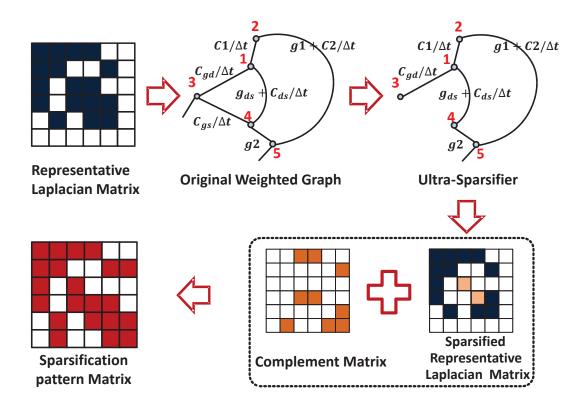

| 2.2  | Circuit MNA matrices decomposed into Laplacian and complement                                                    |    |

|      | matrices                                                                                                         | 20 |

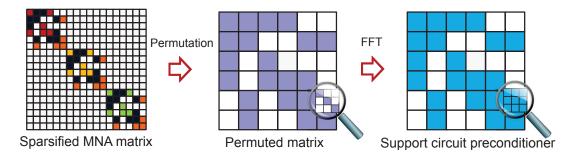

| 2.3  | MNA matrix sparsification pattern                                                                                | 24 |

| 2.4  | HB Jacobian matrix construction                                                                                  | 25 |

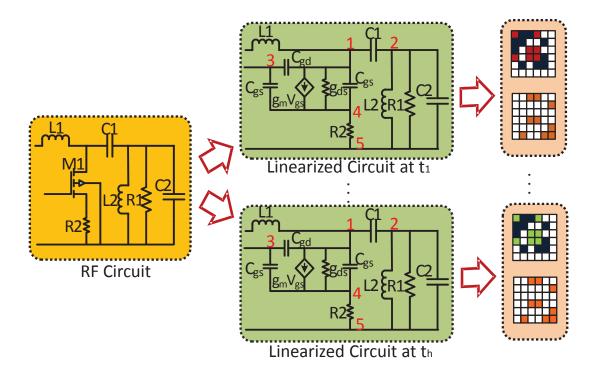

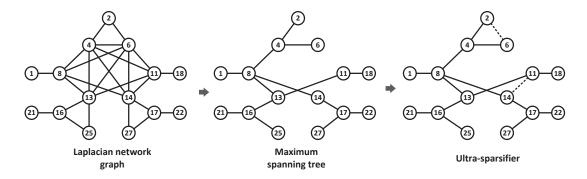

| 2.5  | An RF mixer design (left) and the circuit network (right) corresponding                                          |    |

|      | to its Laplacian matrix                                                                                          | 26 |

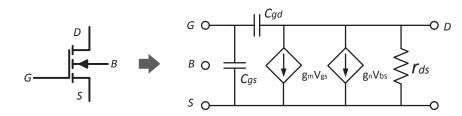

| 2.6  | MOSFET model                                                                                                     | 27 |

| 2.7  | Sparsification of the Laplacian graph of an RF mixer circuit $\ . \ . \ .$                                       | 27 |

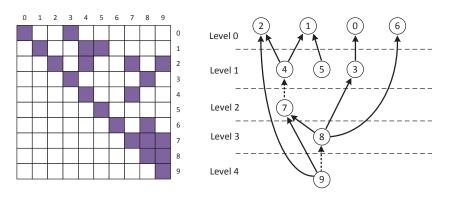

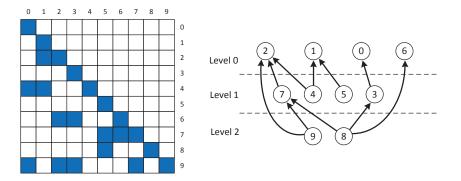

| 2.8  | Upper matrix factor and its DDG                                                                                  | 30 |

| 2.9  | Lower matrix factor and its improved DDG                                                                         | 30 |

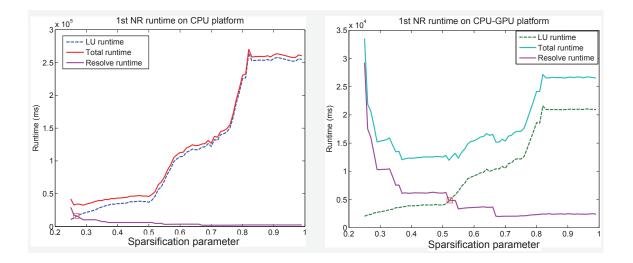

| 2.10 | Runtime profiling for solving two sparsified graphs                                                              | 35 |

| 2.11 | HB simulation runtime with different sparsity $\ldots \ldots \ldots \ldots$                                      | 35 |

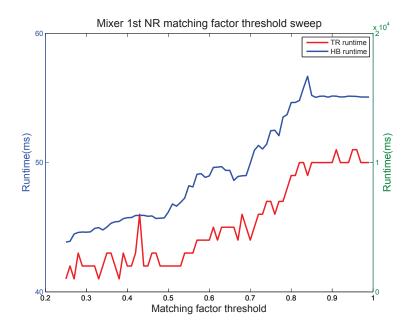

| 2.12 | TR simulation runtime vs. HB simulation runtime                                                                  | 38 |

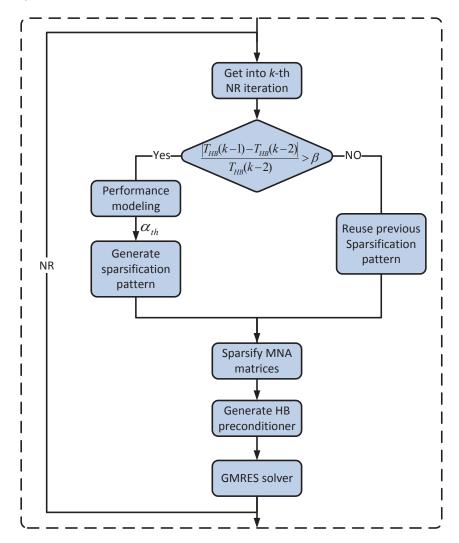

| 2.13 | Performance-guided sparsification scheme                                                                         | 41 |

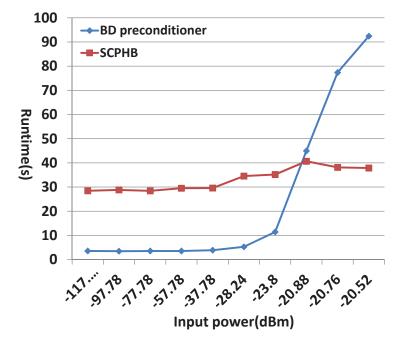

| 2.14 | HB analysis runtime vs. the input power for an RF mixer circuit                                                  | 47 |

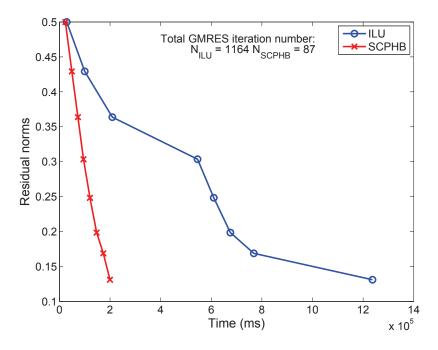

| 2.15 | Convergence rate/time comparisons of SCPHB and ILU algorithms                                                    | 48 |

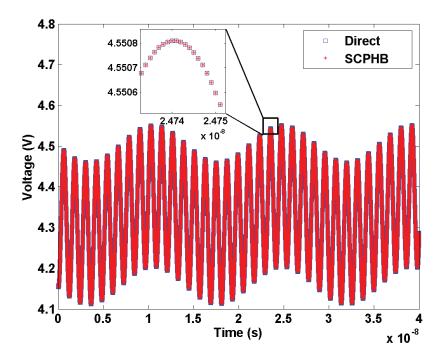

| 2.16 | Waveform result comparison between direct solution method and pro-                                               |    |

|      | posed iterative method $\ldots$ | 49 |

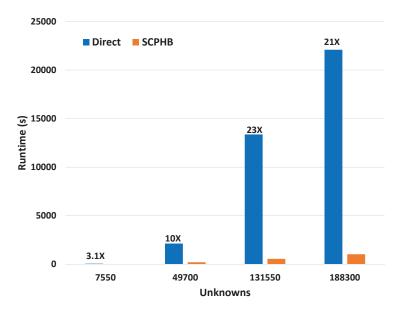

| 2.17 | Results on runtime scalability                                                                                   | 50 |

| 2.18 | Results on memory scalability                                                                                    | 50 |

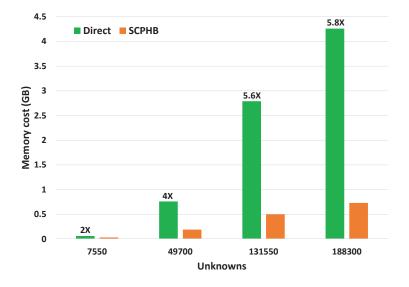

| 3.1  | TinySPICE: massively parallel SPICE simulation program on GPUs          | 54 |

|------|-------------------------------------------------------------------------|----|

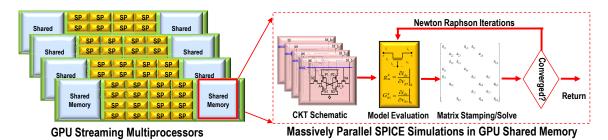

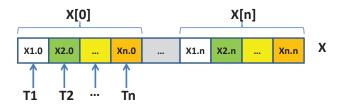

| 3.2  | Vector for storing 3D LUTs                                              | 57 |

| 3.3  | MOSFET stamping location map for dense and sparse matrix format.        |    |

|      |                                                                         | 61 |

| 3.4  | Vectors for storing excitation sources on GPU.                          | 62 |

| 3.5  | Levelized LU factorization task list.                                   | 63 |

| 3.6  | GPU data structure for the LU factorization task list. $\ldots$ .       | 64 |

| 3.7  | Circuit clustering.                                                     | 65 |

| 3.8  | The solution vector data access pattern on GPU                          | 67 |

| 3.9  | The algorithm flow of TinySPICE.                                        | 68 |

| 3.10 | The DC simulation flow of TinySPICE.                                    | 73 |

| 3.11 | TR simulation algorithm flow.                                           | 74 |

| 3.12 | The I-V characteristics obtained by parametric 3D LUT and Bsim4         |    |

|      | model evaluations. Circles denote the LUT evaluation results. $\ . \ .$ | 77 |

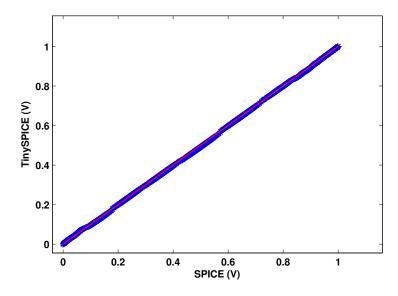

| 3.13 | Scatter plot of the DC simulation results for SRAM circuits obtained    |    |

|      | by TinySPICE and the original Bsim4 SPICE simulator                     | 78 |

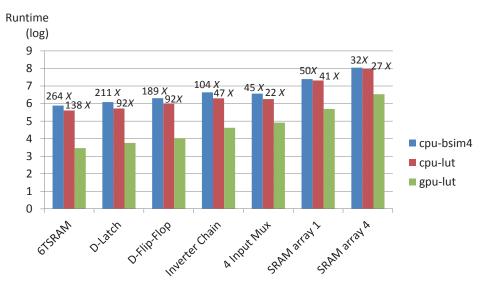

| 3.14 | Comparison of DC Simulation Runtime                                     | 79 |

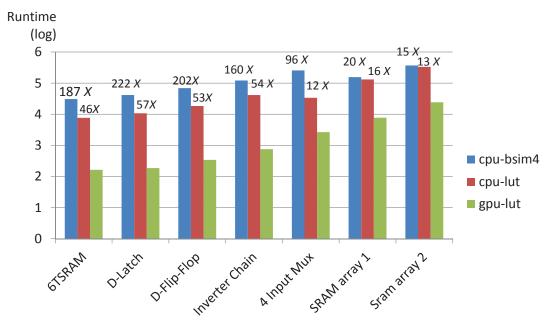

| 3.15 | Comparison of Transient Simulation Runtime                              | 80 |

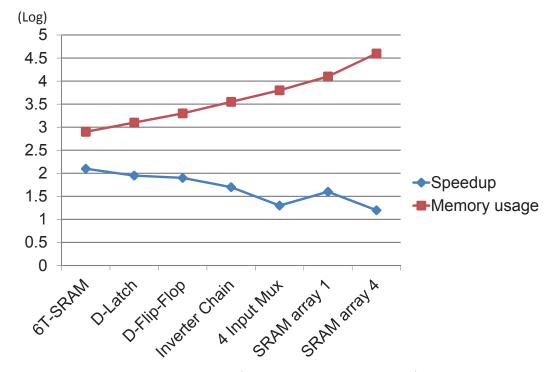

| 3.16 | Memory usage (shared memory + registers) vs. speedups                   | 81 |

# List of Tables

| 2.1 | Experimental circuit descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 44 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Results of runtime and memory cost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45 |

| 3.1 | Experimental setup of test cases.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 76 |

| 3.2 | DC Simulation Runtime Results of TinySPICE with Dense Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 78 |

| 3.3 | Transient Simulation Runtime Results of TinySPICE with Dense For-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|     | mat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 78 |

| 3.4 | $\operatorname{DC}$ simulation runtime results of TinySPICE with sparse format. $% \left( \mathcal{A}_{1}^{\prime}\right) =\left( \mathcal{A}_{1}^{\prime}\right) \left( \mathcal{A}_{1}$ | 81 |

| 3.5 | Transient Simulation Runtime results of TinySPICE with sparse for-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|     | mat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 81 |

### Preface

This dissertation presents my research work in pursuing the PhD degree in Computer Engineering at Michigan Technological University. This dissertation includes previously published articles in Chapter 2 and Chapter 3. All the research works descried herein were conducted under the supervision of my advisor Professor Zhuo Feng.

Chapter 2 contains two articles published in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* and *52nd Design Automation Conference*. As the first author of both papers, with the guidance of my advisor, I completed most parts of algorithm design, implementation, and analysis. Xueqian Zhao, as the second author of the paper published in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, implemented the ultra-sparsifier generation algorithm. The two papers themselves were completed by me and my advisor.

Part of Chapter 3 was published in 50th Design Automation Conference. As the first author, with the guidance of my advisor, I proposed the algorithm and completed its implementation. Xueqian Zhao, as the second author, provided invaluable revision advice of the paper. This article was completed by me and my advisor.

### Acknowledgments

First and foremost, I would like to thank my advisor Professor Zhuo Feng for his support and guidance throughout my stay at Michigan Tech. Professor Feng introduced me to most of the topics presented in this dissertation. Without his continued support, skillful guidance, and insightful advice, most ideas presented in this dissertation would have not materialized. I am also grateful for his encouragement and patience through the ups and downs of my PhD research years.

I would like to thank all my dissertation committee members, Professor Zhenlin Wang, Professor Zhengfu Xu and Professor Kuilin Zhang for their time and invaluable advice during the dissertation process. Thanks to Professor Shiyan Hu for serving on my qualifying examination and proposal committee.

I also want to thank my friends at Michigan Tech, Xueqian Zhao, Caoyang Jiang, Jia Wang, Bojun Ma, Yonghe Guo, Liang Ma, Lin Liu and Yuchen Zhou for their help and supports. Countless discussions with Xueqian Zhao on graph sparsification technology were very helpful to insight me how to apply this new technology to the harmonic balance analysis projects. Caoyang Jiang is always energetic and passionate on discussing the GPU programming techniques.

Finally, and most importantly, I would like to thank my family. Without their unconditioned love and support, it is impossible for me to get this far. My parents are always standing behind me with unending encouragement and support. My wife, Hao Meng, spent lots of time taking care of our family, even when she had her own research work to do. I give my greatest gratitude to her.

### Abstract

Integrated circuit technology has gone through several decades of aggressive scaling. It is increasingly challenging to analyze growing design complexity. Post-layout SPICE simulation can be computationally prohibitive due to the huge amount of parasitic elements, which can easily boost the computation and memory cost. As the decrease in device size, the circuits become more vulnerable to process variations. Designers need to statistically simulate the probability that a circuit does not meet the performance metric, which requires millions times of simulations to capture rare failure events.

Recent, multiprocessors with heterogeneous architecture have emerged as mainstream computing platforms. The heterogeneous computing platform can achieve highthroughput energy efficient computing. However, the application of such platform is not trivial and needs to reinvent existing algorithms to fully utilize the computing resources. This dissertation presents several new algorithms to address those aforementioned two significant and challenging issues on the heterogeneous platform.

Harmonic Balance (HB) analysis is essential for efficient verification of large postlayout RF and microwave integrated circuits (ICs). However, existing methods either suffer from excessively long simulation time and prohibitively large memory consumption or exhibit poor stability. This dissertation introduces a novel transient-simulation guided graph sparsification technique, as well as an efficient runtime performance modeling approach tailored for heterogeneous manycore CPU-GPU computing system to build nearly-optimal subgraph preconditioners that can lead to minimum HB simulation runtime. Additionally, we propose a novel heterogeneous parallel sparse block matrix algorithm by taking advantages of the structure of HB Jacobian matrices as well as GPU's streaming multiprocessors to achieve optimal workload balancing during the preconditioning phase of HB analysis. We also show how the proposed preconditioned iterative algorithm can efficiently adapt to heterogeneous computing systems with different CPU and GPU computing capabilities. Extensive experimental results show that our HB solver can achieve up to 20X speedups and 5X memory reduction when compared with the state-of-the-art direct solver highly optimized for twelve-core CPUs.

In nowadays variation-aware IC designs, cell characterizations and SRAM memory yield analysis require many thousands or even millions of repeated SPICE simulations for relatively small nonlinear circuits. In this dissertation, for the first time, we present a massively parallel SPICE simulator on GPU, TinySPICE, for efficiently analyzing small nonlinear circuits. TinySPICE integrates a highly-optimized shared-memory based matrix solver and fast parametric three-dimensional (3D) LUTs based device evaluation method. A novel circuit clustering method is also proposed to improve the stability and efficiency of the matrix solver. Compared with CPU-based SPICE simulator, TinySPICE achieves up to 264X speedups for parametric SRAM yield analysis without loss of accuracy.

## Chapter 1

# Introduction

As relentless technology scaling reaches into the sub-16nm regime, integrated circuit (IC) designers are facing phenomenal growth of design complexity: present-day multicore/manycore microprocessors integrate billions of transistors into a single chip, while emerging three-dimensional ICs (3D-ICs)[1, 2] integrate multiple active layers in the vertical direction. Key VLSI subsystems such as embedded memory arrays and analog and mixed-signal systems may reach an unprecedented complexity of hundreds of millions of circuit components (nodes), making their modeling, analysis and verification tasks prohibitively expensive and even intractable. It is not rare to experience analog and RF circuit simulations that take a few days or weeks to finish.

Although there has been tremendous evolution in shifting traditional sequential Electronic Design Automation (EDA) tools into their parallel implementations for modern multicore computers in the past decade [3, 4, 5, 6, 7, 8, 9, 10, 11], the future multicore computing will apparently be hindered by the dramatically-increased chip power consumption and slowly-improved heat sinking capability. As a result, present-day computer architects and research community are forced to seek alternative paradigms to sustain ever-increasing performance. The industry realized the only viable solution was to replace some of the large yet power-inefficient general purpose processors by as many as possible slimmers but much more energy-efficient co-processors on the same chip[12], building so-called heterogeneous computing platforms. Recent multiprocessors with such heterogeneous architectures have emerged as mainstream computing platforms, which typically integrate a variety of processing elements of different computing performance, programming flexibility and energy efficiency characteristics. Heterogeneous computing platforms, such as IBM/Sony Cell architectures, personal computers (PCs) with multicore CPUs and manycore GPUs, and the latest low-power heterogeneous microprocessors (e.g. APU from AMD[13], Larrabee from Intel[14], Tegra from Nvidia[15]), can theoretically achieve unprecedented high performance and high energy efficiency simultaneously. With such heterogeneous computing architectures, VLSI CAD developers will face tremendous opportunities to revolutionize EDA industry, thereby targeting much greater performance and energy efficiency.

The goal of this work is to investigate and develop scalable IC modeling, simulation, and verification methods for emerging heterogeneous parallel architectures by reinventing CAD algorithms/data structures and exploiting powerful hardware-specific computing performance/energy modeling and optimization approaches. A coherent set of VLSI CAD problems will be targeted and investigated in this dissertation as followings:

- <sup>†</sup> Scalable post-layout RF circuits harmonic balance analysis

- † Reliability and yield analysis of small circuit

- † Hardware-specific performance modeling for heterogeneous computing architectures

# 1.1 Post-layout RF Circuits Harmonic Balance Analysis

The rapid growth of demand for high-performance wireless systems has increased the need for more efficient, accurate, and robust simulation method for RF circuits. Harmonic balance method is the typical choice for steady state analysis, which can captures the spectral response directly. Traditional HB methods require solving very large yet non-sparse Jacobian matrices, which can take excessively long simulation time and consume a large amount of memory resources when using direct solution methods [16]. As a result, some of existing industrial HB simulators separate the nonlinear and linear parts of the circuit such that the computational cost can be effectively reduced. Unfortunately, such splitting methods assume that the coupling effects between the linear and nonlinear circuit components are relatively weak, and therefore may not be suitable for dealing with large post-layout RF and microwave circuits that involve a lot of parasitics.

To achieve greater computing efficiency than the traditional direct solution methods, several preconditioned Krylov-subspace iterative methods have been investigated and developed in recent years [16, 17, 18, 19]. However, developing high-quality preconditioners for HB analysis has been a very challenging task, since the convergence property of the preconditioned iterative methods for HB analysis strongly depends on the effectiveness of the underlying preconditioners, especially when using the Krylovsubspace iterative methods, such as the GMRES algorithm [20]. For instance, although prior preconditioning methods have shown promising results for trading off the computational efficiency and preconditioning effectiveness, they can be inevitably facing with a variety of limitations and difficulties when handling large and strongly nonlinear post-layout RF and microwave circuits: the block-diagonal averaging preconditioners are easy to compute but only limited to handle weakly nonlinear systems [21]; the hierarchical HB preconditioner proposed in [18] is more effective than the block-diagonal preconditioner and also suitable for parallel computing, but can lead to poor performance or divergence when handling strongly-nonlinear RF ICs since the frequency domain decomposition scheme will introduce large errors during the preconditioning step; another finite-difference Jacobian preconditioner can easily deal with strongly nonlinear systems, but will not work for more than one tones in HB analysis, as discussed in [16]; in a most recent work [16], a sparse block direct solver is developed for solving the Jacobian matrices of HB, but it will consume much more computational resources than iterative methods and cannot scale well with large RF circuit designs. As a result, there is not a preconditioning method that can work robustly for a wide variety of RF and microwave circuits analysis problems, and at the same time be computationally efficient (scalable to large problems sizes). Consequently, it is very desirable to develop efficient yet robust solvers to facilitate fast HB analysis for addressing the challenges in future large-scale RF and microwave IC design and verification procedures.

In this dissertation, recent graph sparsification and support-circuit preconditioning techniques [22, 23, 24, 25] are exploited for developing scalable Jacobian matrix solvers on Heterogeneous platform that can tackle large-scale strongly nonlinear post-layout HB analysis problems. Our approach starts with sparsifying the HB Jacobian matrix with the performance guided sparsification model. We show that the resultant sparsified Jacobian matrix can be used as a robust yet efficient preconditioner in HB analysis. Subsequently, the proposed parallel sparse block solver can solve the preconditioned system rapidly to accelerate the preconditioned Krylov-subspace iterative solving process. Our experimental results show that when compared with the state-of-the-art direct solution method [16], the proposed HB solver can more efficiently handle moderate to strong nonlinearities during the HB analysis of large RF circuits, achieving up to 20X speedups and 5X memory reductions. The main technical contributions of this work have been summarized as follows.

- 1. Proposed a circuit-oriented support-circuit preconditioning approach that can scale almost linearly with large-scale strongly nonlinear post-layout RF circuit.

- 2. Proposed a GPU-friendly sparse block matrix solver for fast solving the preconditioner matrix.

- 3. Proposed a transient-analysis guided hardware-specific graph sparsification scheme to help automatically compute nearly-optimal preconditioners.

#### **1.2** Reliability and Yield Analysis of Small Circuit

Reliability and yield analysis of embedded SRAM memory modules are critical to designs of modern microprocessors, 3D-ICs, and mixed-signal SOCs. However, nanoscale SRAM designs are significantly challenged by prohibitively high computation cost due to the extremely large number of repeated SPICE simulations considering parametric variations [26, 27, 28, 29, 30]. Additionally, current variationaware design methodologies require extremely fast cell/driver characterization capability capturing important process, voltage supply, and temperature (PVT) variations [31, 32], which also demands for much more powerful simulation methodologies. For instance, SRAM readability, writability and stability analysis considering threshold voltage ( $V_{th}$ ), effective channel length ( $L_{eff}$ ) and power supply variations require tens of millions of repeated SPICE simulations for a given design, while variation-aware cell modeling and characterizations also involve constructing look-up tables (LUTs) for capturing all fast/slow corners that require running many thousands of SPICE simulations [31, 32, 33]. Although there have been works that target accelerating SPICE simulations by performing device evaluations on GPU's hundreds of streaming processors and sparse matrix solves on CPU [34], only a small fraction of the computations can be accelerated on GPU, while the overall simulation performance is still limited by the relatively low communication bandwidth and large latency between the CPU and GPU. As a result, only 2X speedups have been obtained when compared with the CPU-based SPICE simulator [34]. Since sparse matrices derived from general nonlinear circuits are typically large scale and asymmetric, no sparse matrix algorithm have been efficiently accelerated on GPU due to a large amount of memory accesses and complicated algorithm flow. Consequently, accelerating the entire computations involved in general-purpose SPICE simulations on GPU remains impractical considering present-day GPU computing limitations. However, there is still a strong need to consider accelerating application-specific SPICE simulations on GPU for achieving much higher computing performance.

In this work, we present a massively parallel SPICE simulator on GPU, TinySPICE, which accelerates the entire SPICE simulation computations on GPU without introducing excessive CPU-GPU data communications and device memory accesses. TinySPICE can analyze small nonlinear circuits in GPU's shared memory and thus gains unprecedentedly high computational throughput. The proposed series of highly-optimized shared-memory based sparse matrix construction and solution techniques allow TinySPICE be able to handle much larger circuits while still being able to achieve orders of magnitude speedup over traditional CPU-based SPICE-like simulation engines. We develop novel GPU-friendly data structures and efficient algorithm flow for every kernel function of the SPICE algorithm that includes device evaluations, matrix construction, linear system solving and Newton-Raphson (NR) iterations. TinySPICE is capable of solving thousands of small circuit simulation problems in GPU's shared memory concurrently, and achieves unprecedented high-performance massively parallel SPICE simulations on GPU. Compared with CPU-based SPICE

simulators, TinySPICE achieves up to 264X speedups for a variety of circuit analysis problems without loss of accuracy. Key contributions of this work have been summarized as follows:

- 1. We propose a massively parallel SPICE simulation engine which is able to perform DC and TR analysis entirely on GPU.

- 2. We propose a series of shared-memory based matrix storage format and matrix solution method to guarantee the simulator can utilize the GPU hardware resources in the most efficient way for different size of circuit designs.

- 3. We propose a novel circuits clustering/classification procedure that will allow to simulate circuits with similar statistical properties (performance) on the same streaming multiprocessor (SM) of each GPU, which can effectively minimize the rounding errors and GPU thread divergences during the sparse matrix factorization procedure.

- 4. We also present a series practical techniques for optimizing GPU's memory usage considering GPU-specific data structures and access patterns to achieve optimal computing throughput.

#### **1.3** Overview of Chapters

This dissertation consists of four chapters. Chapter 1 presents the introduction of the two major problems addressed in this dissertation and the summary of our contributions. Chapter 2 presents the new harmonic balance solver which integrates a novel circuit-oriented preconditioner and parallel sparse block matrix solver. In Chapter 3, the proposed new massively parallel small circuit simulator on GPU is described in details. The dissertation concludes with Chapter 4, which summarizes the work and discuss directions for future research.

## Chapter 2

# Scalable Harmonic Balance Analysis of Post-Layout RF Circuits Leveraging Heterogeneous Platform<sup>1</sup>

### 2.1 Background and Overview

We first review the basics of harmonic balance (HB) method for steady-state simulations of RF circuits. Then, we provide a brief introduction to graph sparsification theory and its applications in developing scalable preconditioned iterative matrix solvers.

<sup>&</sup>lt;sup>1</sup> The material contained in this chapter was previously published in "*IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*" ©2015 IEEE and "*Proceedings of ACM/IEEE Design Automation Conference (DAC)*" ©2015 IEEE. See Appendix A.1 for copies of the copyright permission from IEEE.

#### 2.1.1 Review of Harmonic Balance Analysis

Compared to time-domain analysis that can be obtained by performing transient (TR) circuit simulations, steady-state simulations of RF and microwave circuits typically require HB analysis [16, 17, 18, 19, 21, 35] that can naturally handle frequency-domain data such as S-parameters of linear networks. The basic theory of HB method is introduced as follows. Consider a non-autonomous circuit analysis problem described by the following equation:

$$\int_{-\infty}^{t} y(t-s) x(s) ds + \frac{dq(x(t))}{dt} + f(x(t)) + b(t) = 0, \qquad (2.1)$$

where  $x(t) \in \Re^n$  represents a set of state variables, n is the number of unknowns, y is the matrix-valued impulse response function of frequency-domain linear circuit components (such as S-parameter models),  $q(\bullet)$  denotes a function for the nonlinear charge and flux,  $f(\bullet)$  represents the static (memoryless) nonlinearities, and b represents the time-dependent excitations that are assumed to be periodic with a time period T. The circuit steady-state response x(t), and functions  $q(\bullet)$  as well as  $f(\bullet)$ will be periodic with period T. By writing the above equation in frequency domain and applying Newton-Raphson (NR) method, it can be shown that the linearized system in frequency domain becomes:

$$YX + \Omega\Gamma C\Gamma^{-1}X + \Gamma G\Gamma^{-1}X - B = 0, \qquad (2.2)$$

where X and B denote the Fourier-coefficient vector of x(t) and b(t) respectively,  $\Omega$  is a diagonal matrix denoting the frequency domain differentiation operator,  $\Gamma$  and  $\Gamma^{-1}$ are the fast Fourier transform(FFT) and inverse FFT(IFFT) matrices, while C and G are block diagonal matrices with block diagonals representing the linearizations of  $q(\bullet)$  and  $f(\bullet)$  at h time-domain sampled points that can be described as follows for i = 1, ..., h, respectively:

$$C = diag\left\{c_i = \delta q / \delta x|_{x=x(t_i)}\right\};$$

(2.3)

$$G = diag \left\{ g_i = \left. \delta f / \delta x \right|_{x = x(t_i)} \right\}.$$

(2.4)

When the double-sided FFT/IFFT are used, a total number of h = 2k + 1 harmonics are included to represent each signal, where k is the number of positive frequencies being considered.

In each NR step, a linearized system is solved with a Jacobian matrix of (2.2):

$$J_{hb} = Y + \Omega \Gamma C \Gamma^{-1} + \Gamma G \Gamma^{-1}.$$

(2.5)

The most time-consuming step in HB analysis is the one for solving the large yet non-sparse Jacobian matrix  $J_{hb}$  shown in (2.5). It can be shown that the dense blocks in  $J_{hb}$  are mainly due to the block-circulant matrices  $\Gamma C \Gamma^{-1}$  and  $\Gamma G \Gamma^{-1}$  [21]. For instance, the block-circulant matrix  $\Gamma G \Gamma^{-1}$  can be expressed as:

$$\Gamma \begin{bmatrix} g_1 & & \\ & \ddots & \\ & & g_h \end{bmatrix} \Gamma^{-1} = \begin{bmatrix} G_1 & G_2 & \cdots & G_h \\ G_h & G_1 & \ddots & \vdots \\ \vdots & \ddots & \ddots & G_2 \\ G_2 & \cdots & G_h & G_1 \end{bmatrix}$$

(2.6)

$$= circulant(G_1, \cdots, G_h).$$

As a result, directly solving such a Jacobian matrix using LU-based direct solution method can be very runtime and memory costly due to the very dense matrix structure and a large number of fill-ins introduced during the factorization procedure. Consider a recent state-of-the-art HB simulator developed in [16]. It has been shown that HB analysis of a post-layout RF circuit (LNA+mixer+filter) with 44K nodes and 20 harmonics will result in a Jacobian matrix with more than 1.8 million unknowns that would require around 100 hours and more than 15GB memory when using LUbased direct solution method. On the other hand, the runtime and memory costs for another smaller test case (with half problem size) are 10X less than the previous case, indicating a rather poor algorithm scalability.

To avoid the direct factorization of large and dense Jacobian matrices in HB analysis, iterative methods can be applied to dramatically improve the computing efficiency. Krylov-subspace iterative methods, such as GMRES method [20], are particularly suitable for such problems since only the matrix-vector operations are needed throughout the solution procedures. It has been shown that for HB analysis, the matrix-vector product:

$$JX = YX + \Omega\Gamma C\Gamma^{-1}X + \Gamma G\Gamma^{-1}X \tag{2.7}$$